-

No more parallel bus

- PCI & PCI-X used a shared parallel bus → all devices connected to the same wires and shared bandwidth.

- PCIe uses point-to-point serial links → each device gets its own dedicated path.

-

Software compatibility preserved

- Despite the hardware change, the OS and drivers still see PCIe devices as PCI devices (same config space, enumeration, etc.).

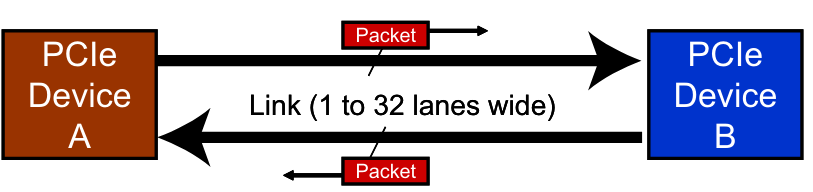

Dual-Simplex Model

- Each connection = two independent paths:

- One Transmit (TX) path (simplex — one direction).

- One Receive (RX) path (simplex — opposite direction).

- Together → behaves like full duplex (data can flow both ways simultaneously).

- PCIe spec calls this dual-simplex (better describes the physical reality: two unidirectional paths).

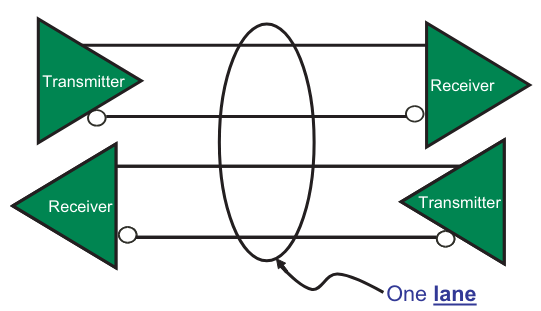

Links and Lanes

- Link: The complete connection between two PCIe devices (e.g., CPU ↔ GPU).

- Lane: A single pair of differential signals (TX+, TX–, RX+, RX–) that can send and receive data.

- Link Width: Number of lanes making up a Link → denoted as:

- x1, x2, x4, x8, x16, x32

- Bandwidth scales with lane count

- More lanes = more throughput, but also higher cost, power, and board space.

Why This Matters

- Scalability: You can tailor bandwidth to the device’s needs.

- Example: a network card might only need x1 or x4, a GPU needs x16.

- Dedicated bandwidth: No more bus contention → no other devices can “steal” your bandwidth.

- Fewer signal integrity issues: Serial differential signaling is easier to scale to high speeds (no clock skew or simultaneous switching noise problems like PCI/PCI-X).